# SWITCHING POWER SUPPLY DESIGN

Abraham I. Pressman Keith Billings Taylor Morey

## **Switching Power Supply Design**

**Third Edition**

Abraham I. Pressman

Keith Billings

Taylor Morey

New York Chicago San Francisco Lisbon London Madrid Mexico City Milan New Delhi San Juan Seoul Singapore Sydney Toronto

#### The McGraw-Hill Companies

#### Library of Congress Cataloging-in-Publication Data

McGraw-Hill books are available at special quantity discounts to use as premiums and sales promotions, or for use in corporate training programs. To contact a special sales representative, please visit the Contact Us page at www.mhprofessional.com.

#### **Switching Power Supply Design, Third Edition**

Copyright © 2009 by The McGraw-Hill Companies.

All rights reserved. Printed in the United States of America. Except as permitted under the Copyright Act of 1976, no part of this publication may be reproduced or distributed in any form or by any means, or stored in a database or retrieval system, without the prior written permission of publisher.

1234567890 DOC DOC 019

ISBN 978-0-07-148272-1 MHID 0-07-148272-5

Sponsoring Editor

Wendy Rinaldi

Acquisitions Coordinator

Joya Anthony

Production Supervisor

George Anderson

Art Director, Cover

Jeff Weeks

Editorial Supervisor

Janet Walden

**Proofreader** Paul Tyler

Composition

International Typesetting and Composition

Cover Designer

Jeff Weeks

**Project Editor** LeeAnn Pickrell

Indexer

Ted Laux

Illustration

International Typesetting and Composition

Information has been obtained by McGraw-Hill from sources believed to be reliable. However, because of the possibility of human or mechanical error by our sources, McGraw-Hill, or others, McGraw-Hill does not guarantee the accuracy, adequacy, or completeness of any information and is not responsible for any errors or omissions or the results obtained from the use of such information.

In fond memory of Abraham Pressman, master of the art, 1915 – 2001. Immortalized by his timeless writings and his legacy—a gift of knowledge for future generations.

To Anne Pressman, for her help and encouragement on the third edition.

To my wife Diana for feeding the brute and allowing him to neglect her, yet again!

### About the Authors

**Abraham I. Pressman** was a nationally known power supply consultant and lecturer. His background ranged from an Army radar officer to over four decades as an analog-digital design engineer in industry. He held key design roles in a number of significant "firsts" in electronics over more than a half century: the first particle accelerator to achieve an energy over one billion volts, the first high-speed printer in the computer industry, the first spacecraft to take pictures of the moon's surface, and two of the earliest textbooks on computer logic circuit design using transistors and switching power supply design, respectively. Mr. Pressman was the author of the first two editions of *Switching Power Supply Design*.

Keith Billings is a Chartered Electronic Engineer and author of the Switchmode Power Supply Handbook, published by McGraw-Hill. Keith spent his early years as an apprentice mechanical instrument maker (at a wage of four pounds a week) and followed this with a period of regular service in the Royal Air Force, servicing navigational instruments including automatic pilots and electronic compass equipment. Keith went into government service in the then Ministry of War and specialized in the design of special test equipment for military applications, including the UK3 satellite. During this period, he became qualified to degree standard by an arduous eight-year stint of evening classes (in those days, the only avenue open to the lower middle-class in England). For the last 44 years, Keith has specialized in switchmode power supply design and manufacturing. At the age of 75, he still remains active in the industry and owns the consulting company DKB Power, Inc., in Guelph, Canada. Keith presents the late Abe Pressman's four-day course on power supply design (now converted to a Power Point presentation) and also a one-day course of his own on magnetics, which is the design of transformers and inductors. He is now a recognized expert in this field. It is a sobering thought to realize he now earns more in one day than he did in a whole year as an apprentice.

Keith was an avid yachtsman for many years, but he now flies gliders as a hobby, having built a high-performance sailplane in 1993. Keith "touched the face of god," achieving an altitude of 22,000 feet in wave lift at Minden, Nevada, in 1994.

**Taylor Morey**, currently a professor of electronics at Conestoga College in Kitchener, Ontario, Canada, is coauthor of an electronics devices textbook and has taught courses at Wilfred Laurier University in Waterloo. He collaborates with Keith Billings as an independent power supply engineer and consultant and previously worked in switchmode power supply development at Varian Canada in Georgetown and Hammond Manufacturing and GFC Power in Guelph, where he first met Keith in 1988. During a five-year sojourn to Mexico, he became fluent in Spanish and taught electronics engineering courses at the Universidad Católica de La Paz and English as a second language at CIBNOR biological research institution of La Paz, where he also worked as an editor of graduate biology students' articles for publication in refereed scientific journals. Earlier in his career, he worked for IBM Canada on mainframe computers and at Global TV's studios in Toronto.

## **Contents**

| Acknowledgments                                                            | xxxiii |

|----------------------------------------------------------------------------|--------|

| Preface                                                                    | XXXV   |

| Part I Topologies                                                          |        |

| 1 Basic Topologies                                                         | 3      |

| 1.1 Introduction to Linear Regulators and Switching Regulators of the Buck | 3      |

| Boost and Inverting Types                                                  |        |

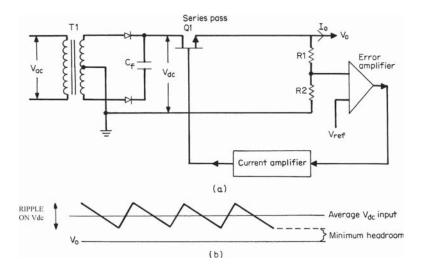

| 1.2 Linear Regulator—the Dissipative Regulator                             | 4      |

| 1.2.1 Basic Operation                                                      | 4      |

| 1.2.2 Some Limitations of the Linear Regulator                             | 6      |

| 1.2.3 Power Dissipation in the Series-Pass Transistor                      | 6<br>7 |

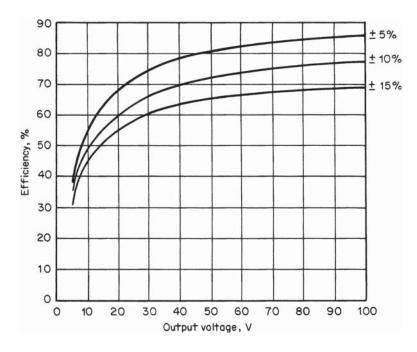

| 1.2.4 Linear Regulator Efficiency vs. Output Voltage                       | 7      |

| 1.2.5 Linear Regulators with PNP Series-Pass Transistors for Reduced       | 9      |

| Dissipation                                                                |        |

| 1.3 Switching Regulator Topologies                                         | 10     |

| 1.3.1 The Buck Switching Regulator                                         | 10     |

| 1.3.1.1 Basic Elements and Waveforms of a Typical Buck Regulator           | 11     |

| 1.3.1.2 Buck Regulator Basic Operation                                     | 13     |

| 1.3.2 Typical Waveforms in the Buck Regulator                              | 14     |

| 1.3.3 Buck Regulator Efficiency                                            | 15     |

| 1.3.3.1 Calculating Conduction Loss and Conduction-Related Efficiency      | 16     |

| 1.3.4 Buck Regulator Efficiency Including AC Switching Losses              | 16     |

| 1.3.5 Selecting the Optimum Switching Frequency                            | 20     |

| 1.3.6 Design Examples                                                      | 21     |

| 1.3.6.1 Buck Regulator Output Filter Inductor (Choke) Design               | 21     |

| 1.3.6.2 Designing the Inductor to Maintain Continuous Mode Operation       | 25     |

| 1.3.6.3 Inductor (Choke) Design                                            | 26     |

|                                                                            |        |

| 1.3.7 Output Capacitor                                                        | 27 |

|-------------------------------------------------------------------------------|----|

| 1.3.8 Obtaining Isolated Semi-Regulated Outputs from a Buck Regulator         | 30 |

| 1.4 The Boost Switching Regulator Topology                                    | 31 |

| 1.4.1 Basic Operation                                                         | 31 |

| 1.4.2 The Discontinuous Mode Action in the Boost Regulator                    | 33 |

| 1.4.3 The Continuous Mode Action in the Boost Regulator                       | 35 |

| 1.4.4 Designing to Ensure Discontinuous Operation in the Boost Regulator      | 37 |

| 1.4.5 The Link Between the Boost Regulator and the Flyback Converter          | 40 |

| 1.5 The Polarity Inverting Boost Regulator                                    | 40 |

| 1.5.1 Basic Operation                                                         | 40 |

| 1.5.2 Design Relations in the Polarity Inverting Boost Regulator              | 42 |

| References                                                                    | 43 |

| 2 Push-Pull and Forward Converter Topologies                                  | 45 |

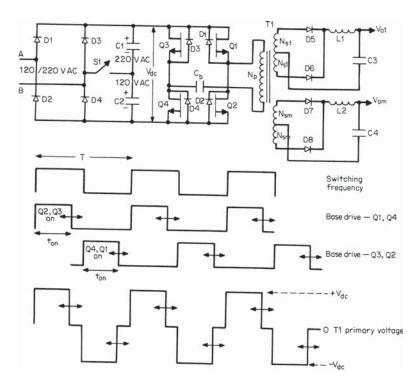

| 2.1 Introduction                                                              | 45 |

| 2.2 The Push-Pull Topology                                                    | 45 |

| 2.2.1 Basic Operation (With Master/Slave Outputs)                             | 45 |

| 2.2.2 Slave Line-Load Regulation                                              | 48 |

| 2.2.3 Slave Output Voltage Tolerance                                          | 49 |

| 2.2.4 Master Output Inductor Minimum Current Limitations                      | 49 |

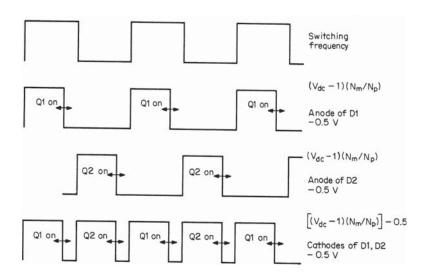

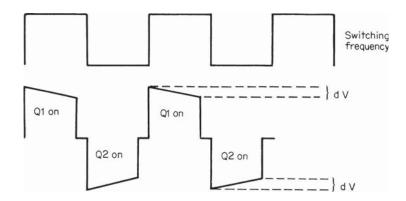

| 2.2.5 Flux Imbalance in the Push-Pull Topology (Staircase Saturation Effects) | 50 |

| 2.2.6 Indications of Flux Imbalance                                           | 52 |

| 2.2.7 Testing for Flux Imbalance                                              | 55 |

| 2.2.8 Coping with Flux Imbalance                                              | 56 |

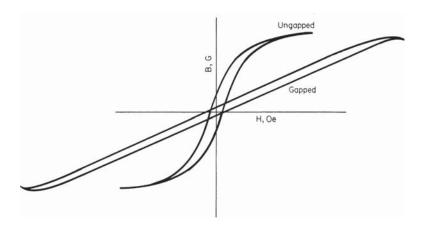

| 2.2.8.1 Gapping the Core                                                      | 56 |

| 2.2.8.2 Adding Primary Resistance                                             | 57 |

| 2.2.8.3 Matching Power Transistors                                            | 57 |

| 2.2.8.4 Using MOSFET Power Transistors                                        | 58 |

| 2.2.8.5 Using Current-Mode Topology                                           | 58 |

| 2.2.9 Power Transformer Design Relationships                                  | 59 |

| 2.2.9.1 Core Selection                                                        | 59 |

| 2.2.9.2 Maximum Power Transistor On-Time Selection                            | 60 |

| 2.2.9.3 Primary Turns Selection                                               | 61 |

| 2.2.9.4 Maximum Flux Change (Flux Density Swing) Selection                    | 61 |

| 2.2.9.5 Secondary Turns Selection                                             | 63 |

| 2.2.10 Primary, Secondary Peak and rms Currents                             | 63 |

|-----------------------------------------------------------------------------|----|

| 2.2.10.1 Primary Peak Current Calculation                                   | 63 |

| 2.2.10.2 Primary rms Current Calculation and Wire Size Selection            | 64 |

| 2.2.10.3 Secondary Peak, rms Current, and Wire Size Calculation             | 65 |

| 2.2.10.4 Primary rms Current, and Wire Size Calculation                     | 66 |

| 2.2.11 Transistor Voltage Stress and Leakage Inductance Spikes              | 67 |

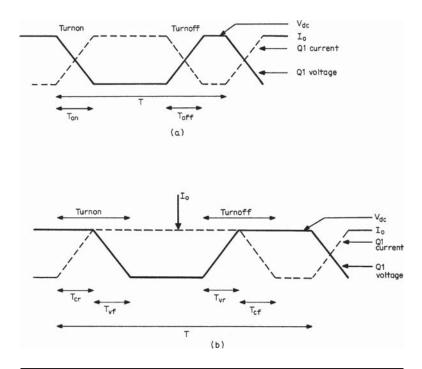

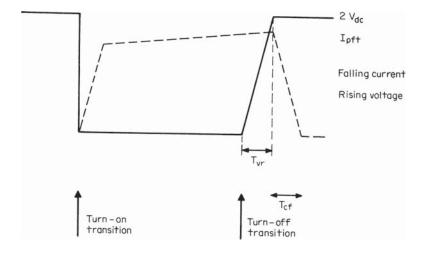

| 2.2.12 Power Transistor Losses                                              | 69 |

| 2.2.12.1 AC Switching or Current-Voltage "Overlap" Losses                   | 69 |

| 2.2.12.2 Transistor Conduction Losses                                       | 70 |

| 2.2.12.3 Typical Losses: 150-W, 50-kHz Push-Pull Converter                  | 71 |

| 2.2.13 Output Power and Input Voltage Limitations in the Push-Pull Topology | 71 |

| 2.2.14 Output Filter Design Relations                                       | 73 |

| 2.2.14.1 Output Inductor Design                                             | 73 |

| 2.2.14.2 Output Capacitor Design                                            | 74 |

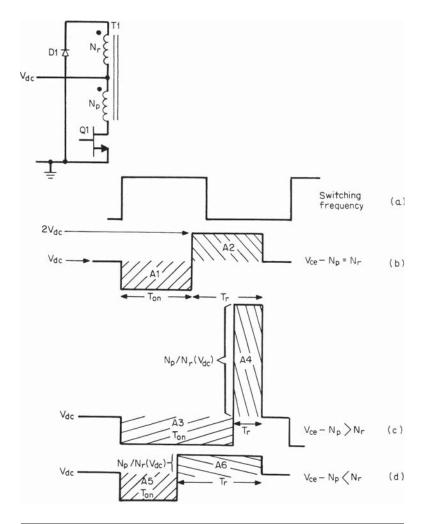

| 2.3 Forward Converter Topology                                              | 75 |

| 2.3.1 Basic Operation                                                       | 75 |

| 2.3.2 Design Relations: Output/Input Voltage, "On" Time, Turns Ratios       | 78 |

| 2.3.3 Slave Output Voltages                                                 | 80 |

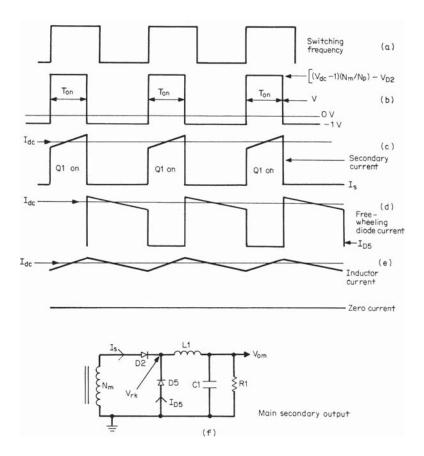

| 2.3.4 Secondary Load, Free-Wheeling Diode, and Inductor Currents            | 81 |

| 2.3.5 Relations Between Primary Current, Output Power, and Input Voltage    | 81 |

| 2.3.6 Maximum Off-Voltage Stress in Power Transistor                        | 82 |

| 2.3.7 Practical Input Voltage/Output Power Limits                           | 83 |

| 2.3.8 Forward Converter With Unequal Power and Reset Winding Turns          | 84 |

| 2.3.9 Forward Converter Magnetics                                           | 86 |

| 2.3.9.1 First-Quadrant Operation Only                                       | 86 |

| 2.3.9.2 Core Gapping in a Forward Converter                                 | 88 |

| 2.3.9.3 Magnetizing Inductance with Gapped Core                             | 89 |

| 2.3.10 Power Transformer Design Relations                                   | 90 |

| 2.3.10.1 Core Selection                                                     | 90 |

| 2.3.10.2 Primary Turns Calculation                                          | 90 |

| 2.3.10.3 Secondary Turns Calculation                                        | 91 |

| 2.3.10.4 Primary rms Current and Wire Size Selection                    | 91  |

|-------------------------------------------------------------------------|-----|

| 2.3.10.5 Secondary rms Current and Wire Size Selection                  | 92  |

| 2.3.10.6 Reset Winding rms Current and Wire Size Selection              | 92  |

| 2.3.11 Output Filter Design Relations                                   | 93  |

| 2.3.11.1 Output Inductor Design                                         | 93  |

| 2.3.11.2 Output Capacitor Design                                        | 94  |

| 2.4 Double-Ended Forward Converter Topology                             | 94  |

| 2.4.1 Basic Operation                                                   | 94  |

| 2.4.1.1 Practical Output Power Limits                                   | 96  |

| 2.4.2 Design Relations and Transformer Design                           | 97  |

| 2.4.2.1 Core Selection—Primary Turns and Wire Size                      | 97  |

| 2.4.2.2 Secondary Turns and Wire Size                                   | 98  |

| 2.4.2.3 Output Filter Design                                            | 98  |

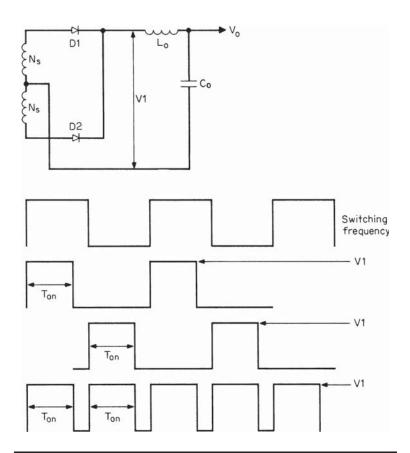

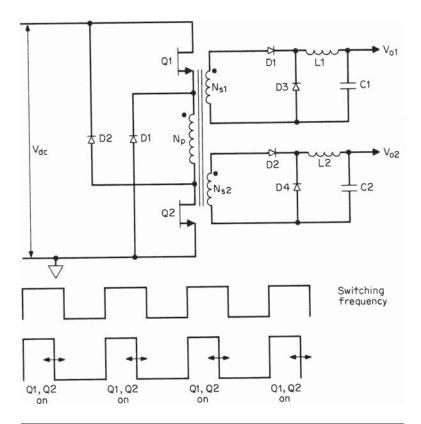

| 2.5 Interleaved Forward Converter Topology                              | 98  |

| 2.5.1 Basic Operation—Merits, Drawbacks, and Output Power Limits        | 98  |

| 2.5.2 Transformer Design Relations                                      | 100 |

| 2.5.2.1 Core Selection                                                  | 100 |

| 2.5.2.2 Primary Turns and Wire Size                                     | 100 |

| 2.5.2.3 Secondary Turns and Wire Size                                   | 101 |

| 2.5.3 Output Filter Design                                              | 101 |

| 2.5.3.1 Output Inductor Design                                          | 101 |

| 2.5.3.2 Output Capacitor Design                                         | 101 |

| Reference                                                               | 101 |

| 3 Half- and Full-Bridge Converter Topologies                            | 103 |

| 3.1 Introduction                                                        | 103 |

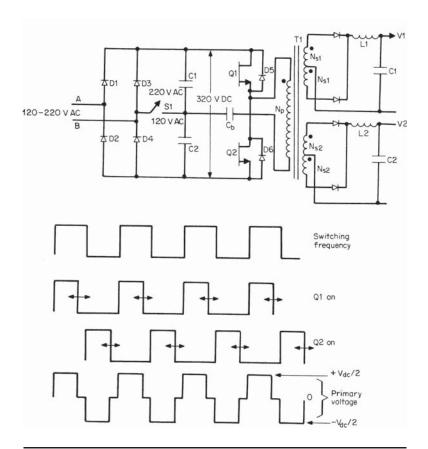

| 3.2 Half-Bridge Converter Topology                                      | 103 |

| 3.2.1 Basic Operation                                                   | 103 |

| 3.2.2 Half-Bridge Magnetics                                             | 105 |

| 3.2.2.1 Selecting Maximum "On" Time, Magnetic Core, and Primary         | 105 |

| Turns                                                                   |     |

| 3.2.2.2 The Relation Between Input Voltage, Primary Current, and Output | 106 |

| Power                                                                   |     |

| 3.2.2.3 Primary Wire Size Selection                                     | 106 |

| 3.2.2.4 Secondary Turns and Wire Size Selection                         | 107 |

| 3.2.3 Output Filter Calculations                                        | 107 |

| 3.2.4 Blocking Capacitor to Avoid Flux Imbalance                        | 107 |

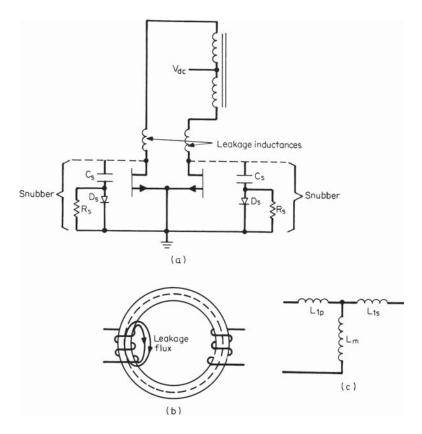

| 3.2.5 Half-Bridge Leakage Inductance Problems                           | 109 |

| 3.2.6 Double-Ended Forward Converter vs. Half Bridge                      | 109 |

|---------------------------------------------------------------------------|-----|

| 3.2.7 Practical Output Power Limits in Half Bridge                        | 111 |

| 3.3 Full-Bridge Converter Topology                                        | 111 |

| 3.3.1 Basic Operation                                                     | 111 |

| 3.3.2 Full-Bridge Magnetics                                               | 113 |

| 3.3.2.1 Maximum "On" Time, Core, and Primary Turns Selection              | 113 |

| 3.3.2.2 Relation Between Input Voltage, Primary Current, and Output Power | 114 |

| 3.3.2.3 Primary Wire Size Selection                                       | 114 |

| 3.3.2.4 Secondary Turns and Wire Size                                     | 114 |

| 3.3.3 Output Filter Calculations                                          | 115 |

| 3.3.4 Transformer Primary Blocking Capacitor                              | 115 |

| 4 Flyback Converter Topologies                                            | 117 |

| 4.1 Introduction                                                          | 120 |

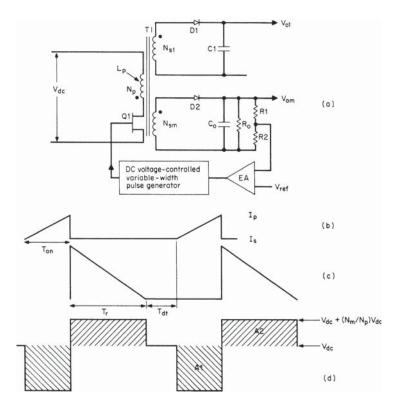

| 4.2 Basic Flyback Converter Schematic                                     | 121 |

| 4.3 Operating Modes                                                       | 121 |

| 4.4 Discontinuous-Mode Operation                                          | 123 |

| 4.4.1 Relationship Between Output Voltage, Input Voltage, "On" Time, and  | 124 |

| Output Load                                                               |     |

| 4.4.2 Discontinuous-Mode to Continuous-Mode Transition                    | 124 |

| 4.4.3 Continuous-Mode Flyback—Basic Operation                             | 127 |

| 4.5 Design Relations and Sequential Design Steps                          | 130 |

| 4.5.1 Step 1: Establish the Primary/Secondary Turns Ratio                 | 130 |

| 4.5.2 Step 2: Ensure the Core Does Not Saturate and the Mode Remains      | 130 |

| Discontinuous                                                             |     |

| 4.5.3 Step 3: Adjust the Primary Inductance Versus Minimum Output         | 131 |

| Resistance and DC Input Voltage                                           |     |

| 4.5.4 Step 4: Check Transistor Peak Current and Maximum Voltage Stress    | 131 |

| 4.5.5 Step 5: Check Primary RMS Current and Establish Wire Size           | 132 |

| 4.5.6 Step 6: Check Secondary RMS Current and Select Wire Size            | 132 |

| 4.6 Design Example for a Discontinuous-Mode Flyback Converter             | 132 |

| 4.6.1 Flyback Magnetics                                                   | 135 |

| 4.6.2 Gapping Ferrite Cores to Avoid Saturation                           | 137 |

|                                                                           |     |

| 4.6.3 Using Powdered Permalloy (MPP) Cores to Avoid Saturation            | 138 |

|---------------------------------------------------------------------------|-----|

| 4.6.4 Flyback Disadvantages                                               | 145 |

| 4.6.4.1 Large Output Voltage Spikes                                       | 145 |

| 4.6.4.2 Large Output Filter Capacitor and High Ripple Current Requirement | 146 |

| 4.7 Universal Input Flybacks for 120-V AC Through 220-V AC Operation      | 147 |

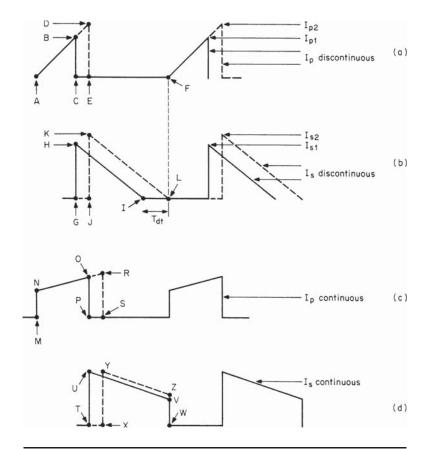

| 4.8 Design Relations—Continuous-Mode Flybacks                             | 149 |

| 4.8.1 The Relation Between Output Voltage and "On" Time                   | 149 |

| 4.8.2 Input, Output Current - Power Relations                             | 150 |

| 4.8.3 Ramp Amplitudes for Continuous Mode at Minimum DC Input             | 152 |

| 4.8.4 Discontinuous- and Continuous-Mode Flyback Design Example           | 153 |

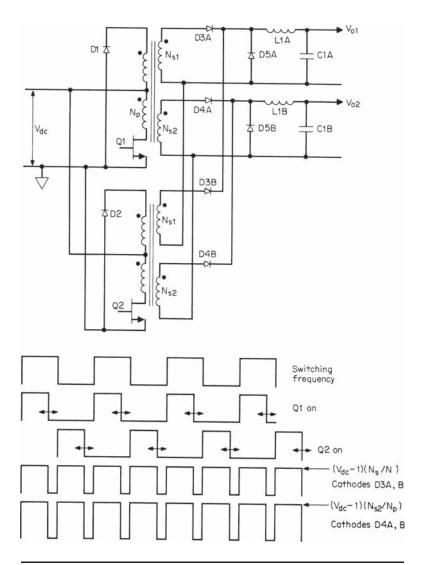

| 4.9 Interleaved Flybacks                                                  | 155 |

| 4.9.1 Summation of Secondary Currents in Interleaved Flybacks             | 156 |

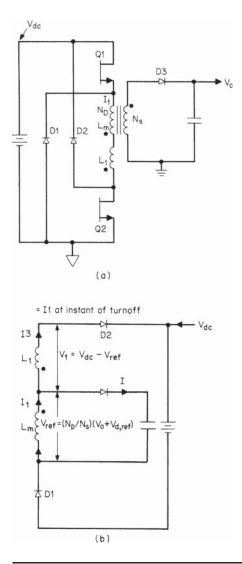

| 4.10 Double-Ended (Two Transistor) Discontinuous-Mode Flyback             | 157 |

| 4.10.1 Area of Application                                                | 157 |

| 4.10.2 Basic Operation                                                    | 157 |

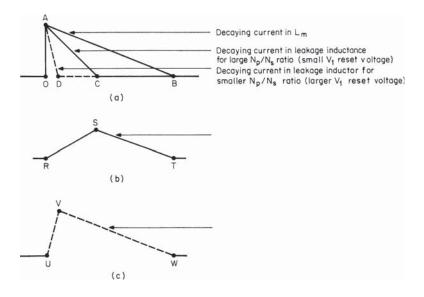

| 4.10.3 Leakage Inductance Effect in Double-Ended Flyback                  | 159 |

| References                                                                | 160 |

| 5 Current-Mode and Current-Fed Topologies                                 | 161 |

| 5.1 Introduction                                                          | 161 |

| 5.1.1 Current-Mode Control                                                | 161 |

| 5.1.2 Current-Fed Topology                                                | 162 |

| 5.2 Current-Mode Control                                                  | 162 |

| 5.2.1 Current-Mode Control Advantages                                     | 163 |

| 5.2.1.1 Avoidance of Flux Imbalance in Push-Pull Converters               | 163 |

| 5.2.1.2 Fast Correction Against Line Voltage Changes Without Error        | 163 |

| Amplifier Delay (Voltage Feed-Forward)                                    |     |

| 5.2.1.3 Ease and Simplicity of Feedback-Loop Stabilization                | 164 |

| 5.2.1.4 Paralleling Outputs                                               | 164 |

| 5.2.1.5 Improved Load Current Regulation                                  | 164 |

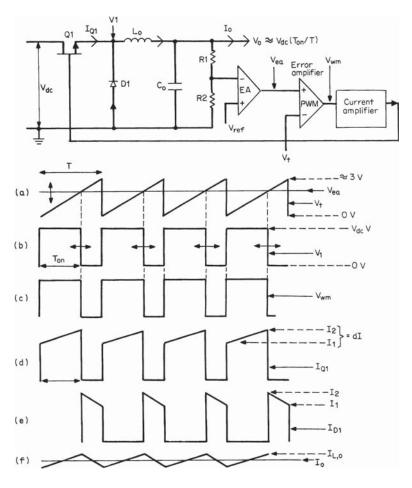

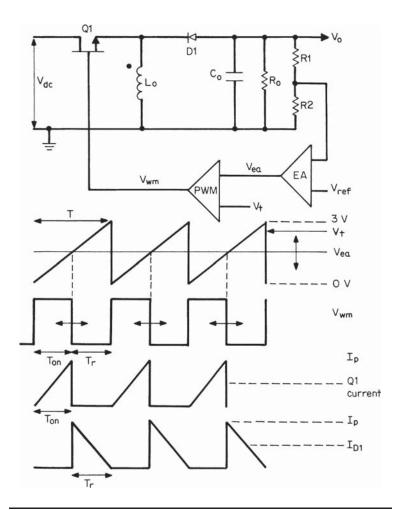

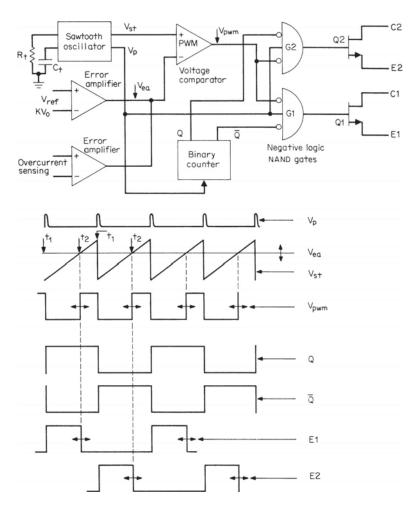

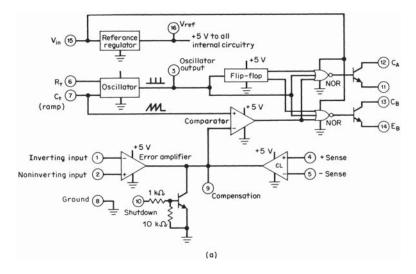

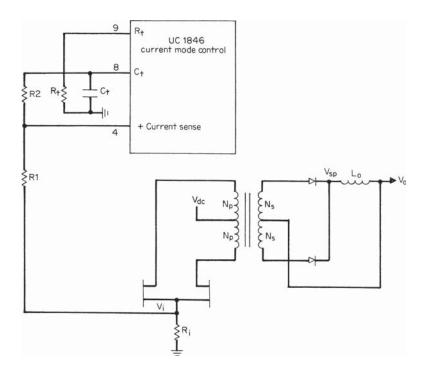

| 5.3 Current-Mode vs. Voltage-Mode Control Circuits                        | 165 |

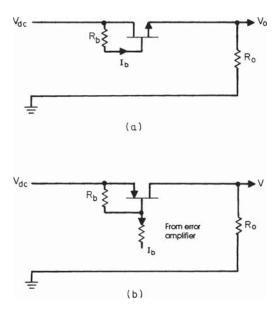

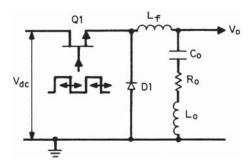

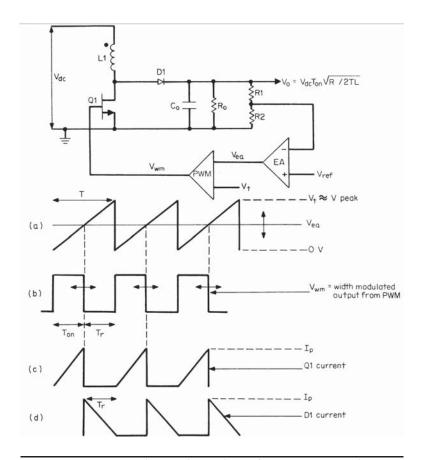

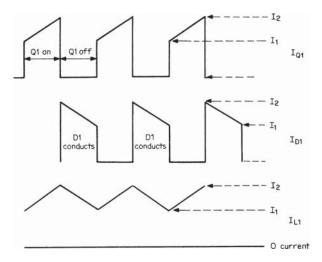

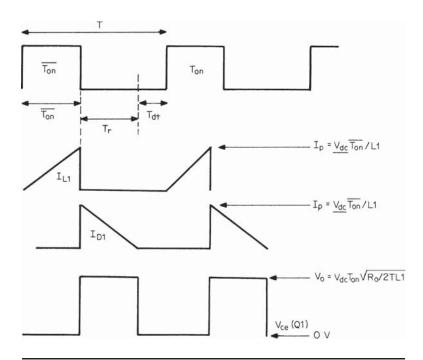

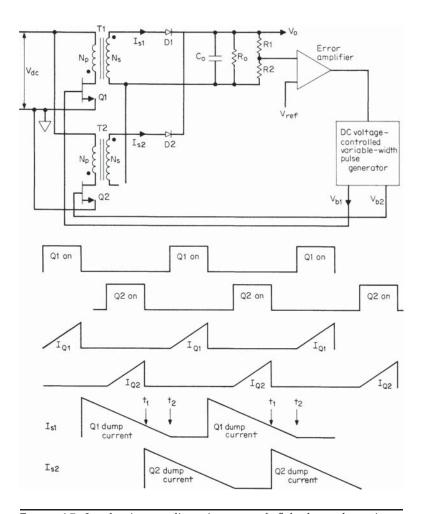

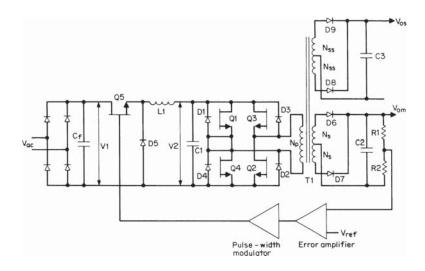

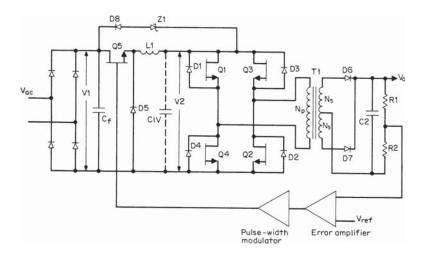

| 5.3.1 Voltage-Mode Control Circuitry                                      | 165 |

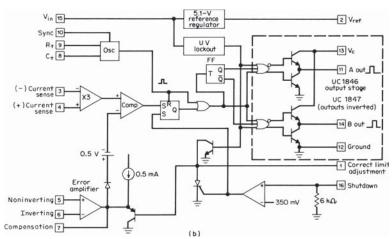

| 5.3.2 Current-Mode Control Circuitry                                      | 169 |

|                                                                           |     |

| 5.4 Detailed Explanation of Current-Mode Advantages                               | 171 |

|-----------------------------------------------------------------------------------|-----|

| 5.4.1 Line Voltage Regulation                                                     | 171 |

| 5.4.2 Elimination of Flux Imbalance                                               | 172 |

| 5.4.3 Simplified Loop Stabilization from Elimination of Output Inductor in Small- | 172 |

| Signal Analysis                                                                   |     |

| 5.4.4 Load Current Regulation                                                     | 174 |

| 5.5 Current-Mode Deficiencies and Limitations                                     | 176 |

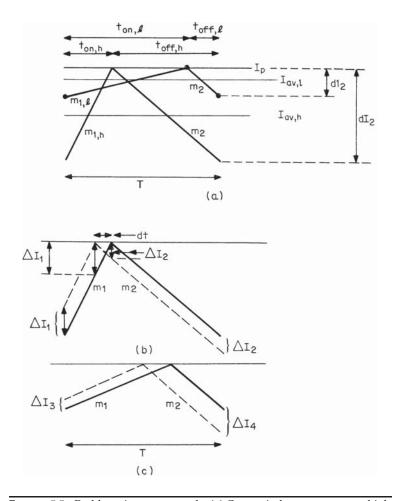

| 5.5.1 Constant Peak Current vs. Average Output Current Ratio Problem              | 176 |

| 5.5.2 Response to an Output Inductor Current Disturbance                          | 179 |

| 5.5.3 Slope Compensation to Correct Problems in Current Mode                      | 179 |

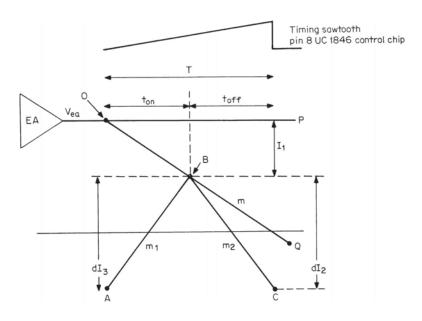

| 5.5.4 Slope (Ramp) Compensation with a Positive-Going Ramp Voltage                | 181 |

| 5.5.5 Implementing Slope Compensation                                             | 182 |

| 5.6 Comparing the Properties of Voltage-Fed and Current-Fed Topologies            | 183 |

| 5.6.1 Introduction and Definitions                                                | 183 |

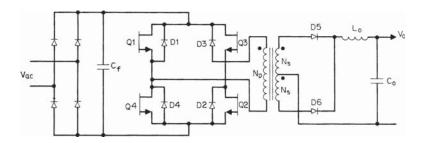

| 5.6.2 Deficiencies of Voltage-Fed, Pulse-Width-Modulated Full-Wave Bridge         | 184 |

| 5.6.2.1 Output Inductor Problems in Voltage-Fed, Pulse-Width-Modulated Full-      | 185 |

| Wave Bridge                                                                       |     |

| 5.6.2.2 Turn "On" Transient Problems in Voltage-Fed, Pulse-Width-                 | 186 |

| Modulated Full-Wave Bridge                                                        |     |

| 5.6.2.3 Turn "Off" Transient Problems in Voltage-Fed, Pulse-Width-                | 187 |

| Modulated Full-Wave Bridge                                                        |     |

| 5.6.2.4 Flux-Imbalance Problem in Voltage-Fed, Pulse-Width-Modulated Full-        | 188 |

| Wave Bridge                                                                       |     |

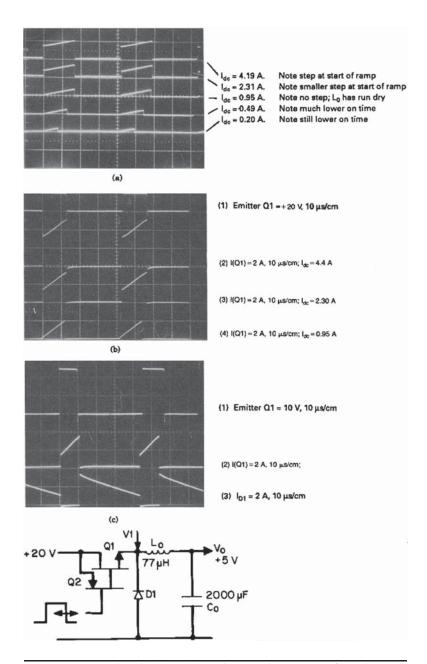

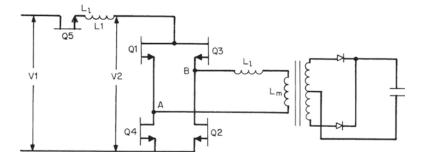

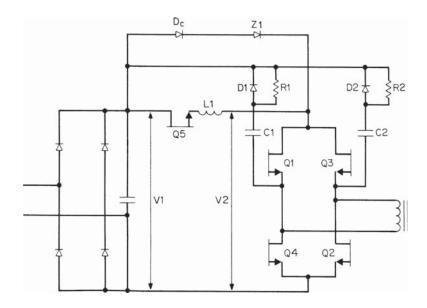

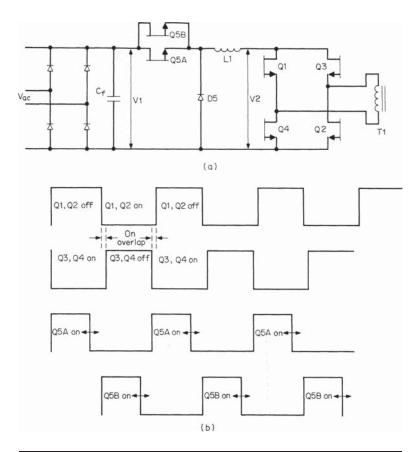

| 5.6.3 Buck Voltage-Fed Full-Wave Bridge Topology—Basic Operation                  | 188 |

| 5.6.4 Buck Voltage-Fed Full-Wave Bridge Advantages                                | 190 |

| 5.6.4.1 Elimination of Output Inductors                                           | 190 |

| 5.6.4.2 Elimination of Bridge Transistor Turn "On" Transients                     | 191 |

| 5.6.4.3 Decrease of Bridge Transistor Turn "Off" Dissipation                      | 192 |

| 5.6.4.4 Flux-Imbalance Problem in Bridge Transformer                              | 192 |

|                                                                                   |     |

| 5.6.5 Drawbacks in Buck Voltage-Fed Full-Wave Bridge                       | 193 |

|----------------------------------------------------------------------------|-----|

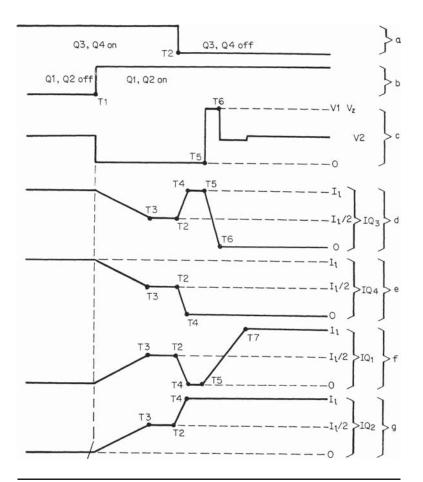

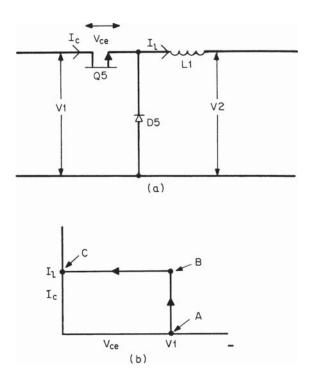

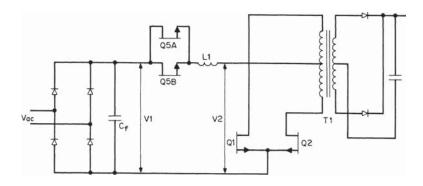

| 5.6.6 Buck Current-Fed Full-Wave Bridge Topology—Basic Operation           | 193 |

| 5.6.6.1 Alleviation of Turn "On" - Turn "Off" Transient Problems in Buck   | 195 |

| Current-Fed Bridge                                                         |     |

| 5.6.6.2 Absence of Simultaneous Conduction Problem in the Buck Current-Fed | 198 |

| Bridge                                                                     |     |

| 5.6.6.3 Turn "On" Problems in Buck Transistor of Buck Current- or Buck     | 198 |

| Voltage-Fed Bridge                                                         |     |

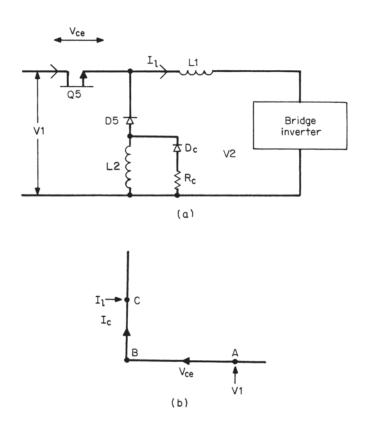

| 5.6.6.4 Buck Transistor Turn "On" Snubber—Basic Operation                  | 201 |

| 5.6.6.5 Selection of Buck Turn "On" Snubber Components                     | 202 |

| 5.6.6.6 Dissipation in Buck Transistor Snubber Resistor                    | 203 |

| 5.6.6.7 Snubbing Inductor Charging Time                                    | 203 |

| 5.6.6.8 Lossless Turn "On" Snubber for Buck Transistor                     | 204 |

| 5.6.6.9 Design Decisions in Buck Current-Fed Bridge                        | 205 |

| 5.6.6.10 Operating Frequencies—Buck and Bridge Transistors                 | 206 |

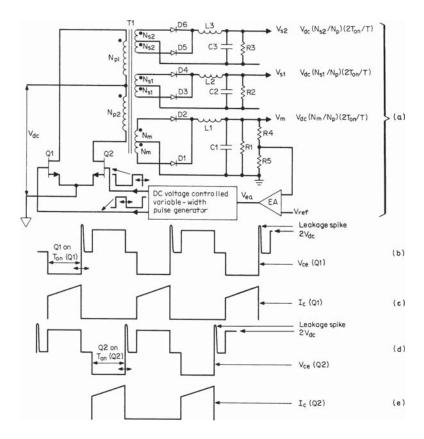

| 5.6.6.11 Buck Current-Fed Push-Pull Topology                               | 206 |

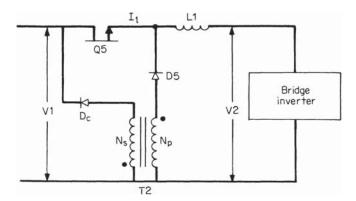

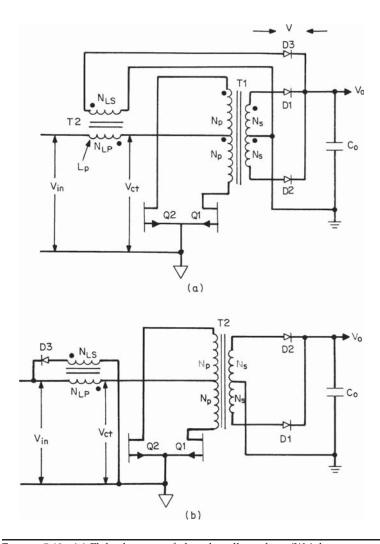

| 5.6.7 Flyback Current-Fed Push-Pull Topology (Weinberg Circuit)            | 208 |

| 5.6.7.1 Absence of Flux-Imbalance Problem in Flyback Current-Fed Push-Pull | 210 |

| Topology                                                                   |     |

| 5.6.7.2 Decreased Push-Pull Transistor Current in Flyback Current-Fed      | 211 |

| Topology                                                                   |     |

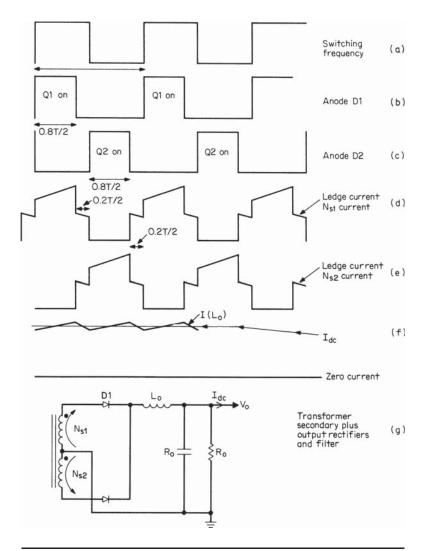

| 5.6.7.3 Non-Overlapping Mode in Flyback Current-Fed Push-Pull Topology—    | 212 |

| Basic Operation                                                            |     |

| 5.6.7.4 Output Voltage vs. "On" Time in Non-Overlapping Mode of Flyback    | 213 |

| Current-Fed Push-Pull Topology                                             |     |

| 5.6.7.5 Output Voltage Ripple and Input Current Ripple in Non-Overlapping  | 214 |

| Mode                                                                       |     |

| 5.6.7.6 Output Stage and Transformer Design Example—Non-Overlapping        | 215 |

| Mode                                                                       |     |

| 5.6.7.7 Flyback Transformer for Design Example of Section 5.6.7.6                        | 218        |

|------------------------------------------------------------------------------------------|------------|

| 5.6.7.8 Overlapping Mode in Flyback Current-Fed Push-Pull Topology—                      | 219        |

| Basic Operation                                                                          |            |

| 5.6.7.9 Output/Input Voltages vs. "On" Time in Overlapping Mode                          | 221        |

| 5.6.7.10 Turns Ratio Selection in Overlapping Mode                                       | 222        |

| 5.6.7.11 Output/Input Voltages vs. "On" Time for Overlap-Mode Design at                  | 223        |

| High DC Input Voltages, with Forced Non-Overlap Operation                                |            |

| 5.6.7.12 Design Example—Overlap Mode                                                     | 224        |

| 5.6.7.13 Voltages, Currents, and Wire Size Selection for Overlap Mode                    | 226        |

| References                                                                               | 227        |

| 6 Miscellaneous Topologies                                                               | 229        |

| 6.1 SCR Resonant Topologies—Introduction                                                 | 229        |

| 6.2 SCR and ASCR Basics                                                                  | 231        |

| 6.3 SCR Turn "Off" by Resonant Sinusoidal Anode Current—Single-Ended                     | 235        |

| Resonant Inverter Topology                                                               | 240        |

| 6.4 SCR Resonant Bridge Topologies—Introduction                                          | 240        |

| 6.4.1 Series-Loaded SCR Half-Bridge Resonant Converter—Basic Operation                   | 241        |

| 6.4.2 Design Calculations—Series-Loaded SCR Half-Bridge Resonant                         | 245        |

| Converter                                                                                | 2.47       |

| 6.4.3 Design Example—Series-Loaded SCR Half-Bridge Resonant Converter                    | 247        |

| 6.4.4 Shunt-Loaded SCR Half-Bridge Resonant Converter                                    | 248        |

| 6.4.5 Single-Ended SCR Resonant Converter Topology Design                                | 249        |

| 6.4.5.1 Minimum Trigger Period Selection                                                 | 251        |

| 6.4.5.2 Peak SCR Current Choice and <i>LC</i> Component Selection 6.4.5.3 Design Example | 252<br>253 |

| 6.4.3.3 Design Example 6.5 Cuk Converter Topology—Introduction                           | 253        |

| 6.5.1 Cuk Converter—Basic Operation                                                      | 255        |

| 6.5.2 Relation Between Output and Input Voltages, and Q1 "On" Time                       | 256        |

| 6.5.3 Rates of Change of Current in L1, L2                                               | 257        |

| 6.5.4 Reducing Input Ripple Currents to Zero                                             | 258        |

| 6.5.5 Isolated Outputs in the Cuk Converter                                              | 259        |

| 0.5.5 Isolated Sulputs in the Car Convertor                                              | 25)        |

| 6.6 Low Output Power "Housekeeping" or "Auxiliary" Topologies—                                     | 260 |

|----------------------------------------------------------------------------------------------------|-----|

| Introduction                                                                                       |     |

| 6.6.1 Housekeeping Power Supply—on Output or Input Common?                                         | 261 |

| 6.6.2 Housekeeping Supply Alternatives                                                             | 262 |

| 6.6.3 Specific Housekeeping Supply Block Diagrams                                                  | 262 |

| 6.6.3.1 Housekeeping Supply for AC Prime Power                                                     | 262 |

| 6.6.3.2 Oscillator-Type Housekeeping Supply for AC Prime Power                                     | 264 |

| 6.6.3.3 Flyback-Type Housekeeping Supplies for DC Prime Power                                      | 265 |

| 6.6.4 Royer Oscillator Housekeeping Supply—Basic Operation                                         | 266 |

| 6.6.4.1 Royer Oscillator Drawbacks                                                                 | 268 |

| 6.6.4.2 Current-Fed Royer Oscillator                                                               | 271 |

| 6.6.4.3 Buck Preregulated Current-Fed Royer Converter                                              | 271 |

| 6.6.4.4 Square Hysteresis Loop Materials for Royer Oscillators                                     | 274 |

| 6.6.4.5 Future Potential for Current-Fed Royer and Buck Preregulated                               | 277 |

| Current-Fed Royer                                                                                  |     |

| 6.6.5 Minimum-Parts-Count Flyback as Housekeeping Supply                                           | 278 |

| 6.6.6 Buck Regulator with DC-Isolated Output as a Housekeeping Supply                              | 280 |

| References                                                                                         | 280 |

| Part II Magnetics and Circuit Design                                                               |     |

| 7 Transformers and Magnetic Design                                                                 | 285 |

| 7.1 Introduction                                                                                   | 285 |

| 7.2 Transformer Core Materials and Geometries and Peak Flux Density Selection                      | 286 |

| 7.2.1 Ferrite Core Losses versus Frequency and Flux Density for Widely Used Core Materials         | 286 |

| 7.2.2 Ferrite Core Geometries                                                                      | 289 |

| 7.2.3 Peak Flux Density Selection                                                                  | 294 |

| 7.3 Maximum Core Output Power, Peak Flux Density, Core and Bobbin Areas, and Coil Currency Density | 295 |

| 7.3.1 Derivation of Output Power Relations for Converter Topology                                  | 295 |

| 7.3.2 Derivation of Output Power Relations for Push-Pull Topology             | 299 |

|-------------------------------------------------------------------------------|-----|

| 7.3.2.1 Core and Copper Losses in Push-Pull, Forward Converter Topologies     | 301 |

| 7.3.2.2 Doubling Output Power from a Given Core Without Resorting to a Push-  | 302 |

| Pull Topology                                                                 |     |

| 7.3.3 Derivation of Output Power Relations for Half Bridge Topology           | 304 |

| 7.3.4 Output Power Relations in Full Bridge Topology                          | 306 |

| 7.3.5 Conversion of Output Power Equations into Charts Permitting Core and    | 306 |

| Operating Frequency Selection at a Glance                                     |     |

| 7.3.5.1 Peak Flux Density Selection at Higher Frequencies                     | 314 |

| 7.4 Transformer Temperature Rise Calculations                                 | 315 |

| 7.5 Transformer Copper Losses                                                 | 320 |

| 7.5.1 Introduction                                                            | 320 |

| 7.5.2 Skin Effect                                                             | 321 |

| 7.5.3 Skin Effect—Quantitative Relations                                      | 323 |

| 7.5.4 AC/DC Resistance Ratio for Various Wire Sizes at Various Frequencies    | 324 |

| 7.5.5 Skin Effect with Rectangular Current Waveshapes                         | 327 |

| 7.5.6 Proximity Effect                                                        | 328 |

| 7.5.6.1 Mechanism of Proximity Effect                                         | 328 |

| 7.5.6.2 Proximity Effect Between Adjacent Layers in a Transformer Coil        | 330 |

| 7.5.6.3 Proximity Effect AC/DC Resistance Ratios from Dowell Curves           | 333 |

| 7.6 Introduction: Inductor and Magnetics Design Using the Area Product Method | 338 |

| 7.6.1 The Area Product Figure of Merit                                        | 339 |

| 7.6.2 Inductor Design                                                         | 340 |

| 7.6.3 Low Power Signal-Level Inductors                                        | 340 |

| 7.6.4 Line Filter Inductors                                                   | 341 |

| 7.6.4.1 Common-Mode Line Filter Inductors                                     | 341 |

| 7.6.4.2 Toroidal Core Common-Mode Line Filter Inductors                       | 341 |

| 7.6.4.3 E Core Common-Mode Line Filter Inductors                              | 344 |

| 7.6.5 Design Example: Common-Mode 60 Hz Line Filter                           | 345 |

| 7.6.5.1 Step 1: Select Core Size and Establish Area Product                 | 345 |

|-----------------------------------------------------------------------------|-----|

| 7.6.5.2 Step 2: Establish Thermal Resistance and Internal Dissipation Limit | 347 |

| 7.6.5.3 Step 3: Establish Winding Resistance                                | 348 |

| 7.6.5.4 Step 4: Establish Turns and Wire Gauge from the Nomogram Shown in   | 349 |

| Figure 7.15                                                                 |     |

| 7.6.5.5 Step 5: Calculating Turns and Wire Gauge                            | 349 |

| 7.6.6 Series-Mode Line Filter Inductors                                     | 352 |

| 7.6.6.1 Ferrite and Iron Powder Rod Core Inductors                          | 353 |

| 7.6.6.2 High-Frequency Performance of Rod Core Inductors                    | 355 |

| 7.6.6.3 Calculating Inductance of Rod Core Inductors                        | 356 |

| 7.7 Magnetics: Introduction to Chokes—Inductors with Large DC Bias Current  | 358 |

| 7.7.1 Equations, Units, and Charts                                          | 359 |

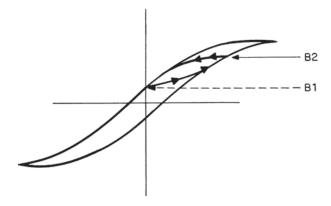

| 7.7.2 Magnetization Characteristics (B/H Loop) with DC Bias Current         | 359 |

| 7.7.3 Magnetizing Force $H_{dc}$                                            | 361 |

| 7.7.4 Methods of Increasing Choke Inductance or Bias Current Rating         | 362 |

| 7.7.5 Flux Density Swing $\Delta B$                                         | 363 |

| 7.7.6 Air Gap Function                                                      | 366 |

| 7.7.7 Temperature Rise                                                      | 367 |

| 7.8 Magnetics Design: Materials for Chokes—Introduction                     | 367 |

| 7.8.1 Choke Materials for Low AC Stress Applications                        | 368 |

| 7.8.2 Choke Materials for High AC Stress Applications                       | 368 |

| 7.8.3 Choke Materials for Mid-Range Applications                            | 369 |

| 7.8.4 Core Material Saturation Characteristics                              | 369 |

| 7.8.5 Core Material Loss Characteristics                                    | 370 |

| 7.8.6 Material Saturation Characteristics                                   | 371 |

| 7.8.7 Material Permeability Parameters                                      | 371 |

| 7.8.8 Material Cost                                                         | 373 |

| 7.8.9 Establishing Optimum Core Size and Shape                              | 374 |

| 7.8.10 Conclusions on Core Material Selection                               | 374 |

| 7.9 Magnetics: Choke Design Examples                                        | 375 |

| 7.9.1 Choke Design Example: Gapped Ferrite E Core                           | 375 |

|                                                                             |     |

| 7.9.2 Step 1: Establish Inductance for 20% Ripple Current                  | 376 |

|----------------------------------------------------------------------------|-----|

| 7.9.3 Step 2: Establish Area Product (AP)                                  | 377 |

| 7.9.4 Step 3: Calculate Minimum Turns                                      | 378 |

| 7.9.5 Step 4: Calculate Core Gap                                           | 378 |

| 7.9.6 Step 5: Establish Optimum Wire Size                                  | 380 |

| 7.9.7 Step 6: Calculating Optimum Wire Size                                | 381 |

| 7.9.8 Step 7: Calculate Winding Resistance                                 | 382 |

| 7.9.9 Step 8: Establish Power Loss                                         | 382 |

| 7.9.10 Step 9: Predict Temperature Rise—Area Product Method                | 383 |

| 7.9.11 Step 10: Check Core Loss                                            | 383 |

| 7.10 Magnetics: Choke Designs Using Powder Core Materials—Introduction     | 387 |

| 7.10.1 Factors Controlling Choice of Powder Core Material                  | 388 |

| 7.10.2 Powder Core Saturation Properties                                   | 388 |

| 7.10.3 Powder Core Material Loss Properties                                | 389 |

| 7.10.4 Copper Loss - Limited Choke Designs for Low AC Stress               | 391 |

| 7.10.5 Core Loss - Limited Choke Designs for High AC Stress                | 392 |

| 7.10.6 Choke Designs for Medium AC Stress                                  | 392 |

| 7.10.7 Core Material Saturation Properties                                 | 393 |

| 7.10.8 Core Geometry                                                       | 393 |

| 7.10.9 Material Cost                                                       | 394 |

| 7.11 Choke Design Example: Copper Loss Limited Using Kool Mµ Powder Toroid | 395 |

| 7.11.1 Introduction                                                        | 395 |

| 7.11.2 Selecting Core Size by Energy Storage and Area Product Methods      | 395 |

| 7.11.3 Copper Loss - Limited Choke Design Example                          | 397 |

| 7.11.3.1 Step 1: Calculate Energy Storage Number                           | 397 |

| 7.11.3.2 Step 2: Establish Area Product and Select Core Size               | 397 |

| 7.11.3.3 Step 3: Calculate Initial Turns                                   | 397 |

| 7.11.3.4 Step 4: Calculate DC Magnetizing Force                            | 399 |

| 7.11.3.5 Step 5: Establish New Relative Permeability and Adjust Turns      | 399 |

| 7.11.3.6 Step 6: Establish Wire Size                                       | 399 |

| 7.11.3.7 Step 7: Establish Copper Loss                                     | 400 |

| 7.11.3.8 Step 8: Check Temperature Rise by Energy Density Method           | 400 |

| 7 11 2 0 Store O. Dradict Tomas continue Disc by Area Draduct Mathed                                    | 401        |

|---------------------------------------------------------------------------------------------------------|------------|

| 7.11.3.9 Step 9: Predict Temperature Rise by Area Product Method 7.11.3.10 Step 10: Establish Core Loss | 401<br>401 |

| 1                                                                                                       | 401        |

| 7.12 Choke Design Examples Using Various Powder E Cores 7.12.1 Introduction                             | 403        |

|                                                                                                         | 403        |

| 7.12.2 First Example: Choke Using a #40 Iron Powder E Core                                              | 404        |

| 7.12.2.1 Step 1: Calculate Inductance for 1.5 Amps Ripple Current                                       | 404        |

| 7.12.2.2 Step 2: Calculate Energy Storage Number                                                        | 400        |

| 7.12.2.3 Step 3: Establish Area Product and Select Core Size                                            |            |

| 7.12.2.4 Step 4: Calculate Initial Turns                                                                | 407        |

| 7.12.2.5 Step 5: Calculate Core Loss                                                                    | 409        |

| 7.12.2.6 Step 6: Establish Wire Size                                                                    | 411        |

| 7.12.2.7 Step 7: Establish Copper Loss                                                                  | 411        |

| 7.12.3 Second Example: Choke Using a #8 Iron Powder E Core                                              | 412        |

| 7.12.3.1 Step 1: Calculate New Turns                                                                    | 412        |

| 7.12.3.2 Step 2: Calculate Core Loss with #8 Mix                                                        | 412        |

| 7.12.3.3 Step 3: Establish Copper Loss                                                                  | 413        |

| 7.12.3.4 Step 4: Calculate Efficiency and Temperature Rise                                              | 413        |

| 7.12.4 Third Example: Choke Using #60 Kool Mμ E Cores                                                   | 413        |

| 7.12.4.1 Step 1: Select Core Size                                                                       | 414        |

| 7.12.4.2 Step 2: Calculate Turns                                                                        | 414        |

| 7.12.4.3 Step 3: Calculate DC Magnetizing Force                                                         | 415        |

| 7.12.4.4 Step 4: Establish Relative Permeability and Adjust Turns                                       | 415        |

| 7.12.4.5 Step 5: Calculate Core Loss with #60 Kool Mµ Mix                                               | 415        |

| 7.12.4.6 Step 6: Establish Wire Size                                                                    | 416        |

| 7.12.4.7 Step 7: Establish Copper Loss                                                                  | 416        |

| 7.12.4.8 Step 8: Establish Temperature Rise                                                             | 416        |

| 7.13 Swinging Choke Design Example: Copper Loss Limited Using Kool Mµ                                   | 417        |

| Powder E Core                                                                                           |            |

| 7.13.1 Swinging Chokes                                                                                  | 417        |

| 7.13.2 Swinging Choke Design Example                                                                    | 418        |

| 7.13.2.1 Step 1: Calculate Energy Storage Number                                                        | 418        |

|                                                                                                         |            |

| 7.13.2.2 Step 2: Establish Area Product and Select Core Size                     | 418 |

|----------------------------------------------------------------------------------|-----|

| 7.13.2.3 Step 3: Calculate Turns for 100 Oersteds                                | 419 |

| 7.13.2.4 Step 4: Calculate Inductance                                            | 419 |

| 7.13.2.5 Step 5: Calculate Wire Size                                             | 420 |

| 7.13.2.6 Step 6: Establish Copper Loss                                           | 420 |

| 7.13.2.7 Step 7: Check Temperature Rise by Thermal Resistance Method             | 420 |

| 7.13.2.8 Step 8: Establish Core Loss                                             | 421 |

| References                                                                       | 421 |

| 8 Bipolar Power Transistor Base Drive Circuits                                   | 423 |

| 8.1 Introduction                                                                 | 423 |

| 8.2 The Key Objectives of Good Base Drive Circuits for Bipolar Transistors       | 424 |

| 8.2.1 Sufficiently High Current Throughout the "On" Time                         | 424 |

| 8.2.2 A Spike of High Base Input Current $I_{b1}$ at Instant of Turn "On"        | 425 |

| 8.2.3 A Spike of High Reverse Base Current $I_{b2}$ at the Instant of Turn "Off" | 427 |

| (Figure 8.2 <i>a</i> )                                                           |     |

| 8.2.4 A Base-to-Emitter Reverse Voltage Spike –1 to –5 V in Amplitude at the     | 427 |

| Instant of Turn "Off"                                                            |     |

| 8.2.5 The Baker Clamp (A Circuit That Works Equally Well with High-or Low-       | 429 |

| Beta Transistors)                                                                |     |

| 8.2.6 Improving Drive Efficiency                                                 | 429 |

| 8.3 Transformer Coupled Baker Clamp Circuits                                     | 430 |

| 8.3.1 Baker Clamp Operation                                                      | 431 |

| 8.3.2 Transformer Coupling into a Baker Clamp                                    | 435 |

| 8.3.2.1 Transformer Supply Voltage, Turns Ratio Selection, and Primary and       | 435 |

| Secondary Current Limiting                                                       |     |

| 8.3.2.2 Power Transistor Reverse Base Current Derived from Flyback Action        | 437 |

| in Drive Transformer                                                             |     |

| 8.3.2.3 Drive Transformer Primary Current Limiting to Achieve Equal              | 438 |

| Forward and Reverse Base Currents in Power Transistor at End of the "On"         |     |

| Time                                                                             |     |

| 8.3.2.4 Design Example—Transformer-Driven Baker Clamp                            | 439 |

| 8.3.3 Baker Clamp with Integral Transformer                                                           | 440        |

|-------------------------------------------------------------------------------------------------------|------------|

| 8.3.3.1 Design Example—Transformer Baker Clamp                                                        | 442        |

| 8.3.4 Inherent Baker Clamping with a Darlington Transistor                                            | 442        |

| 8.3.5 Proportional Base Drive                                                                         | 443        |

| 8.3.5.1 Detailed Circuit Operation—Proportional Base Drive                                            | 443        |

| 8.3.5.2 Quantitative Design of Proportional Base Drive Scheme                                         | 446        |

| 8.3.5.3 Selection of Holdup Capacitor (C1, Figure 8.12) to Guarantee Power Transistor Turn "Off"      | 447        |

| 8.3.5.4 Base Drive Transformer Primary Inductance and Core Selection                                  | 449        |

| 8.3.5.5 Design Example—Proportional Base Drive                                                        | 449        |

| 8.3.6 Miscellaneous Base Drive Schemes                                                                | 450        |

| References                                                                                            | 455        |

| 9 MOSFET and IGBT Power Transistors and Gate Drive Requirements                                       | 457        |

| 9.1 MOSFET Introduction                                                                               | 457        |

| 9.1.1 IGBT Introduction                                                                               | 457        |

| 9.1.2 The Changing Industry                                                                           | 458        |

| 9.1.3 The Impact on New Designs                                                                       | 458        |

| 9.2 MOSFET Basics                                                                                     | 459        |

| 9.2.1 Typical Drain Current vs. Drain-to-Source Voltage Characteristics ( $I_d$                       | 461        |

| $V_{\rm ds}$ ) for a FET Device                                                                       |            |

| 9.2.2 "On" State Resistance $r_{ds}$ (on)                                                             | 461        |

| 9.2.3 MOSFET Input Impedance Miller Effect and Required Gate Currents                                 | 464        |

| 9.2.4 Calculating the Gate Voltage Rise and Fall Times for a Desired Drain Current Rise and Fall Time | 467        |

| 9.2.5 MOSFET Gate Drive Circuits                                                                      | 468        |

| 9.2.6 MOSFET $R_{ds}$ Temperature Characteristics and Safe Operating Area                             | 473        |

| Limits                                                                                                |            |

| 9.2.7 MOSFET Gate Threshold Voltage and Temperature Characteristics                                   | 475        |

| 9.2.8 MOSFET Switching Speed and Temperature Characteristics                                          | 476        |

| 9.2.9 MOSFET Current Ratings                                                                          | 477        |

| 9.2.10 Paralleling MOSFETs                                                                            | 480        |

| 9.2.11 MOSFETs in Push-Pull Topology                                                                  | 483        |

| 9.2.12 MOSFET Maximum Gate Voltage Specifications 9.2.13 MOSFET Drain-to-Source, "Body," Diode        | 484<br>485 |

| 9 / L3 MUNEET Drain-to-Source Body Diode                                                              | 4×>        |

| 9.3 Introduction to Insulated Gate Bipolar Transistors (IGBTs)             | 487 |

|----------------------------------------------------------------------------|-----|

| 9.3.1 Selecting Suitable IGBTs for Your Application                        | 488 |

| 9.3.2 IGBT Construction Overview                                           | 489 |

| 9.3.2.1 Equivalent Circuits                                                | 490 |

| 9.3.3 Performance Characteristics of IGBTs                                 | 490 |

| 9.3.3.1 Turn "Off" Characteristics of IGBTs                                | 490 |

| 9.3.3.2 The Difference Between PT- and NPT-Type IGBTs                      | 491 |

| 9.3.3.3 The Conduction of PT- and NPT-Type IGBTs                           | 491 |

| 9.3.3.4 The Link Between Ruggedness and Switching Loss in PT- and NPT-     | 491 |

| Type IGBTs                                                                 |     |

| 9.3.3.5 IGBT Latch-Up Possibilities                                        | 492 |

| 9.3.3.6 Temperature Effects                                                | 493 |

| 9.3.4 Parallel Operation of IGBTs                                          | 493 |

| 9.3.5 Specification Parameters and Maximum Ratings                         | 494 |

| 9.3.6 Static Electrical Characteristics                                    | 498 |

| 9.3.7 Dynamic Characteristics                                              | 499 |

| 9.3.8 Thermal and Mechanical Characteristics                               | 504 |

| References                                                                 | 509 |

| 10 Magnetic-Amplifier Postregulators                                       | 511 |

| 10.1 Introduction                                                          | 511 |

| 10.2 Linear and Buck Postregulators                                        | 513 |

| 10.3 Magnetic Amplifiers—Introduction                                      | 513 |

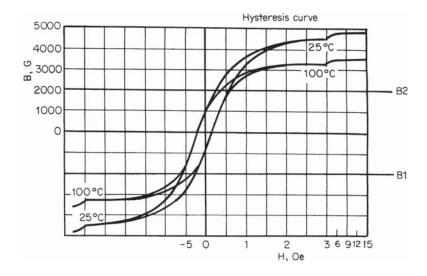

| 10.3.1 Square Hysteresis Loop Magnetic Core as a Fast Acting On/Off Switch | 516 |

| with Electrically Adjustable "On" and "Off" Times                          |     |

| 10.3.2 Blocking and Firing Times in Magnetic-Amplifier Postregulators      | 519 |

| 10.3.3 Magnetic-Amplifier Core Resetting and Voltage Regulation            | 520 |

| 10.3.4 Slave Output Voltage Shutdown with Magnetic Amplifiers              | 521 |

| 10.3.5 Square Hysteresis Loop Core Characteristics and Sources             | 522 |

| 10.3.6 Core Loss and Temperature Rise Calculations                         | 529 |

| 10.3.7 Design Example—Magnetic-Amplifier Postregulator                     | 534 |

| 10.3.8 Magnetic-Amplifier Gain                                             | 539 |

|----------------------------------------------------------------------------|-----|

| 10.3.9 Magnetic Amplifiers for a Push-Pull Output                          | 540 |

| 10.4 Magnetic Amplifier Pulse-Width Modulator and Error Amplifier          | 540 |

| 10.4.1 Circuit Details, Magnetic Amplifier Pulse-Width Modulator - Error   | 541 |

| Amplifier                                                                  |     |

| References                                                                 | 544 |

| 11 Analysis of Turn "On" and Turn "Off" Switching Losses and the Design    | 545 |

| of Load-Line Shaping Snubber Circuits                                      |     |

| 11.1 Introduction                                                          | 545 |

| 11.2 Transistor Turn "Off" Losses Without a Snubber                        | 547 |

| 11.3 RCD Turn "Off" Snubber Operation                                      | 548 |

| 11.4 Selection of Capacitor Size in <i>RCD</i> Snubber                     | 550 |

| 11.5 Design Example— <i>RCD</i> Snubber                                    | 551 |

| 11.5.1 <i>RCD</i> Snubber Returned to Positive Supply Rail                 | 552 |

| 11.6 Non-Dissipative Snubbers                                              | 553 |

| 11.7 Load-Line Shaping (The Snubber's Ability to Reduce Spike Voltages so  | 555 |

| as to Avoid Secondary Breakdown)                                           |     |

| 11.8 Transformer Lossless Snubber Circuit                                  | 558 |

| References                                                                 | 559 |

| 12 Feedback Loop Stabilization                                             | 561 |

| 12.1 Introduction                                                          | 561 |

| 12.2 Mechanism of Loop Oscillation                                         | 563 |

| 12.2.1 The Gain Criterion for a Stable Circuit                             | 563 |

| 12.2.2 Gain Slope Criteria for a Stable Circuit                            | 563 |

| 12.2.3 Gain Characteristic of Output LC Filter with and without Equivalent | 567 |

| Series Resistance (ESR) in Output Capacitor                                |     |

| 12.2.4 Pulse-Width-Modulator Gain                                          | 570 |

| 12.2.5 Gain of Output LC Filter Plus Modulator and Sampling Network        | 571 |

| 12.3 Shaping Error-Amplifier Gain Versus Frequency Characteristic          | 572 |

| 12.4 Error-Amplifier Transfer Function, Poles, and Zeros                   | 575 |

| 12.5 Rules for Gain Slope Changes Due to Zeros and Poles                   | 576 |

|                                                                            |     |

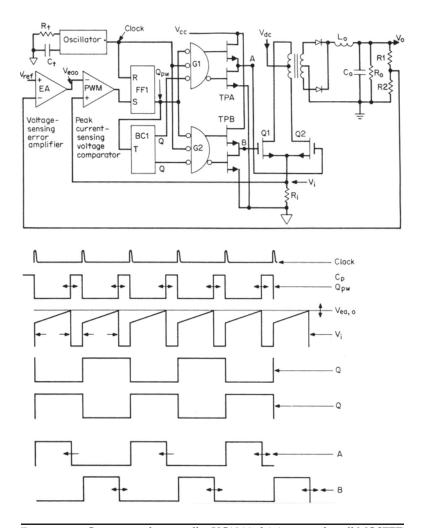

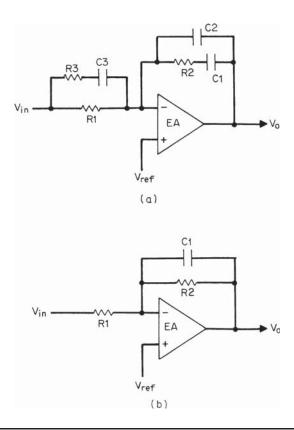

| 12.6 Derivation of Transfer Function of an Error Amplifier with Single Zero and Single Pole from Its Schematic | 578         |

|----------------------------------------------------------------------------------------------------------------|-------------|

| 12.7 Calculation of Type 2 Error-Amplifier Phase Shift from Its Zero and Pole                                  | 579         |

| Locations                                                                                                      | <b>5</b> 00 |

| 12.8 Phase Shift Through LC Filter with Significant ESR                                                        | 580         |

| 12.9 Design Example—Stabilizing a Forward Converter Feedback Loop with a                                       | 582         |

| Type 2 Error Amplifier                                                                                         | 505         |

| 12.10 Type 3 Error Amplifier—Application and Transfer Function                                                 | 585         |

| 12.11 Phase Lag Through a Type 3 Error Amplifier as Function of Zero and                                       | 587         |

| Pole Locations                                                                                                 | <b>-</b> 00 |

| 12.12 Type 3 Error Amplifier Schematic, Transfer Function, and Zero and Pole                                   | 588         |

| Locations                                                                                                      | <b>7</b> 00 |

| 12.13 Design Example—Stabilizing a Forward Converter Feedback Loop with a                                      | 590         |

| Type 3 Error Amplifier                                                                                         | <b>700</b>  |

| 12.14 Component Selection to Yield Desired Type 3 Error-Amplifier Gain                                         | 592         |

| Curve                                                                                                          | <b>700</b>  |

| 12.15 Conditional Stability in Feedback Loops                                                                  | 593         |

| 12.16 Stabilizing a Discontinuous-Mode Flyback Converter                                                       | 595         |

| 12.16.1 DC Gain from Error-Amplifier Output to Output Voltage Node                                             | 595         |

| 12.16.2 Discontinuous-Mode Flyback Transfer Function from Error-Amplifier                                      | 597         |

| Output to Output Voltage Node                                                                                  |             |

| 12.17 Error-Amplifier Transfer Function for Discontinuous-Mode Flyback                                         | 599         |

| 12.18 Design Example—Stabilizing a Discontinuous-Mode Flyback Converter                                        | 600         |

| 12.19 Transconductance Error Amplifiers                                                                        | 602         |

| References                                                                                                     | 605         |

| 13 Resonant Converters                                                                                         | 607         |

| 13.1 Introduction                                                                                              | 607         |

| 13.2 Resonant Converters                                                                                       | 608         |

| 13.3 The Resonant Forward Converter                                                                            | 609         |

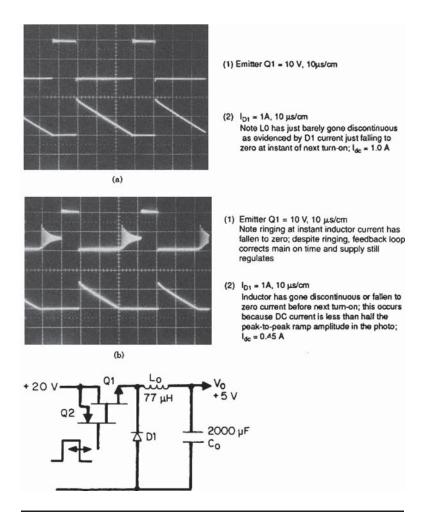

| 13.3.1 Measured Waveforms in a Resonant Forward Converter                                                      | 612         |

| 13.4 Resonant Converter Operating Modes                                                                        | 614         |

| 13.4.1 Discontinuous and Continuous: Operating Modes Above and Below                                           | 614         |

| Resonance                                                                                                      |             |

| 13.5 Resonant Half Bridge in Continuous-Conduction Mode                     | 616 |

|-----------------------------------------------------------------------------|-----|

| 13.5.1 Parallel Resonant Converter (PRC) and Series Resonant Converter      | 616 |

| (SRC)                                                                       |     |

| 13.5.2 AC Equivalent Circuits and Gain Curves for Series-Loaded and         | 619 |

| Parallel-Loaded Half Bridges Operating in the Continuous-Conduction Mode    |     |

| 13.5.3 Regulation with Series-Loaded Half Bridge in Continuous-Conduction   | 620 |

| Mode (CCM)                                                                  |     |

| 13.5.4 Regulation with a Parallel-Loaded Half Bridge in the Continuous-     | 621 |

| Conduction Mode                                                             |     |

| 13.5.5 Series-Parallel Resonant Converter in Continuous-Conduction Mode     | 622 |

| 13.5.6 Zero-Voltage-Switching Quasi-Resonant (CCM) Converters               | 623 |

| 13.6 Resonant Power Supplies—Conclusion                                     | 627 |

| References                                                                  | 628 |

| Part III Waveforms                                                          |     |

| 14 Typical Waveforms for Switching Power Supplies                           | 631 |

| 14.1 Introduction                                                           | 631 |

| 14.2 Forward Converter Waveshapes                                           | 632 |

| 14.2.1 $V_{ds}$ , $I_d$ Photos at 80% of Full Load                          | 633 |

| 14.2.2 $V_{ds}$ , $I_d$ Photos at 40% of Full Load                          | 635 |

| 14.2.3 Overlap of Drain Voltage and Drain Current at Turn "On" /Turn        | 635 |

| "Off" Transitions                                                           |     |

| 14.2.4 Relative Timing of Drain Current, Drain-to-Source Voltage, and Gate- | 638 |

| to-Source Voltage                                                           |     |

| 14.2.5 Relationship of Input Voltage to Output Inductor, Output Inductor    | 638 |

| Current Rise and Fall Times, and Power Transistor Drain-Source Voltage      |     |

| 14.2.6 Relative Timing of Critical Waveforms in PWM Driver Chip             | 639 |

| (UC3525A) for Forward Converter of Figure 14.1                              |     |

| 14.3 Push-Pull Topology Waveshapes—Introduction                             | 640 |

| 14.3.1 Transformer Center Tap Currents and Drain-to-Source Voltages at      | 642 |

| Maximum Load Currents for Maximum, Nominal, and Minimum Supply              |     |

| Voltages                                                                    |     |

| 14.3.2 Opposing $V_{ds}$ Waveshapes, Relative Timing, and Flux Locus During Dead                                              | 644          |

|-------------------------------------------------------------------------------------------------------------------------------|--------------|

| Time                                                                                                                          |              |

| 14.3.3 Relative Timing of Gate Input Voltage, Drain-to-Source Voltage, and                                                    | 647          |

| Drain Currents                                                                                                                |              |

| 14.3.4 Drain Current Measured with a Current Probe in the Drain Compared to                                                   | 647          |

| that Measured with a Current Probe in the Transformer Center Tap                                                              |              |

| 14.3.5 Output Ripple Voltage and Rectifier Cathode Voltage                                                                    | 647          |

| 14.3.6 Oscillatory Ringing at Rectifier Cathodes after Transistor Turn "On"                                                   | 650          |

| 14.3.7 AC Switching Loss Due to Overlap of Falling Drain Current and Rising                                                   | 650          |

| Drain Voltage at Turn "Off"                                                                                                   |              |

| 14.3.8 Drain Currents as Measured in the Transformer Center Tap and Drain-to-                                                 | 652          |

| Source Voltage at One-Fifth of Maximum Output Power                                                                           |              |

| 14.3.9 Drain Current and Voltage at One-Fifth Maximum Output Power                                                            | 655          |

| 14.3.10 Relative Timing of Opposing Drain Voltages at One-Fifth Maximum                                                       | 655          |

| Output Currents                                                                                                               |              |

| 14.3.11 Controlled Output Inductor Current and Rectifier Cathode Voltage                                                      | 656          |

| 14.3.12 Controlled Rectifier Cathode Voltage Above Minimum Output Current                                                     | 656          |

| 14.3.13 Gate Voltage and Drain Current Timing                                                                                 | 656          |

| 14.3.14 Rectifier Diode and Transformer Secondary Currents                                                                    | 656          |

| 14.3.15 Apparent Double Turn "On" per Half Period Arising from Excessive                                                      | 658          |

| Magnetizing Current or Insufficient Output Currents 14.3.16 Drain Currents and Voltages at 15% Above Specified Maximum Output | 659          |

| Power                                                                                                                         | 039          |

| 14.3.17 Ringing at Drain During Transistor Dead Time                                                                          | 659          |

| 14.4 Flyback Topology Waveshapes                                                                                              | 660          |

| 14.4.1 Introduction                                                                                                           | 660          |

| 14.4.2 Drain Current and Voltage Waveshapes at 90% of Full Load for Minimum,                                                  | 662          |

| Nominal, and Maximum Input Voltages                                                                                           | 5 3 <b>2</b> |

| 14.4.3 Voltage and Currents at Output Rectifier Inputs                                                                        | 662          |

|                                                                                                                               |              |

| 14.4.4 Snubber Capacitor Current at Transistor Turn "Off"                        | 665        |

|----------------------------------------------------------------------------------|------------|

| References                                                                       | 666        |

| Part IV More Recent Applications for Switching Power Supply Techniques           |            |

| 15 Power Factor and Power Factor Correction                                      | 669        |

| 15.1 Power Factor—What Is It and Why Must It Be Corrected?                       | 669        |

| 15.2 Power Factor Correction in Switching Power Supplies                         | 671        |

| 15.3 Power Factor Correction—Basic Circuit Details                               | 673        |

| 15.3.1 Continuous- Versus Discontinuous-Mode Boost Topology for Power            | 676        |

| Factor Correction                                                                |            |

| 15.3.2 Line Input Voltage Regulation in Continuous-Mode Boost Converters         | 678        |

| 15.3.3 Load Current Regulation in Continuous-Mode Boost Regulators               | 679        |

| 15.4 Integrated-Circuit Chips for Power Factor Correction                        | 681        |

| 15.4.1 The Unitrode UC 3854 Power Factor Correction Chip                         | 681        |

| 15.4.2 Forcing Sinusoidal Line Current with the UC 3854                          | 682        |

| 15.4.3 Maintaining Constant Output Voltage with UC 3854                          | 684        |

| 15.4.4 Controlling Power Output with the UC 3854                                 | 685        |

| 15.4.5 Boost Switching Frequency with the UC 3854                                | 687        |

| 15.4.6 Selection of Boost Output Inductor <i>L1</i>                              | 687        |

| 15.4.7 Selection of Boost Output Capacitor                                       | 688        |

| 15.4.8 Peak Current Limiting in the UC 3854                                      | 690        |

| 15.4.9 Stabilizing the UC 3854 Feedback Loop                                     | 690        |

| 15.5 The Motorola MC 34261 Power Factor Correction Chip                          | 691        |

| 15.5.1 More Details of the Motorola MC 34261 (Figure 15.11)                      | 693        |

| 15.5.2 Logic Details for the MC 34261 (Figures 15.11 and 15.12)                  | 693        |

| 15.5.3 Calculations for Frequency and Inductor L1                                | 694        |

| 15.5.4 Selection of Sensing and Multiplier Resistors for the MC 34261 References | 696<br>697 |

| INCICICIOCS                                                                      | 09/        |

| 16 Electronic Ballasts: High-Frequency Power Regulators for Fluorescent Lamps 69 | 99        |

|----------------------------------------------------------------------------------|-----------|

|                                                                                  | 99        |

| 16.2 Fluorescent Lamp—Physics and Types 70                                       | 03        |

| 16.3 Electric Arc Characteristics 70                                             | 06        |

| 16.3.1 Arc Characteristics with DC Supply Voltage 70                             | 07        |

| 16.3.2 AC-Driven Fluorescent Lamps 70                                            | 09        |

| 16.3.3 Fluorescent Lamp Volt/Ampere Characteristics with an Electronic 7         | 11        |

| Ballast                                                                          |           |

| 16.4 Electronic Ballast Circuits 7                                               | 15        |

| 16.5 DC/AC Inverter—General Characteristics 7                                    | 16        |

| 16.6 DC/AC Inverter Topologies 7                                                 | 17        |

| 16.6.1 Current-Fed Push-Pull Topology 7                                          | 18        |

| 16.6.2 Voltage and Currents in Current-Fed Push-Pull Topology 7/2                | 20        |

| 16.6.3 Magnitude of "Current Feed" Inductor in Current-Fed Topology 72           | 21        |

| 16.6.4 Specific Core Selection for Current Feed Inductor                         | 22        |

| 16.6.5 Coil Design for Current Feed Inductor                                     | 29        |

| 16.6.6 Ferrite Core Transformer for Current-Fed Topology 72                      | 29        |

| 16.6.7 Toroidal Core Transformer for Current-Fed Topology 73                     | 37        |

| 16.7 Voltage-Fed Push-Pull Topology 73                                           | 37        |

|                                                                                  | 40        |

| 16.9 Voltage-Fed Series Resonant Half Bridge Topology 74                         | 42        |

| 16.10 Electronic Ballast Packaging 74                                            | 45        |